# FORRIONS

DESIGN TRADEOFFS IN STACK COMPUTERS

A 32-BIT FORTH ENGINE

PHASE ANGLE DIFFERENCE ANALYZER

INTERPRETATION MACROS

ANS FORTH: HARDWARE INDEPENDENCE

# SILICON COMPOSERS

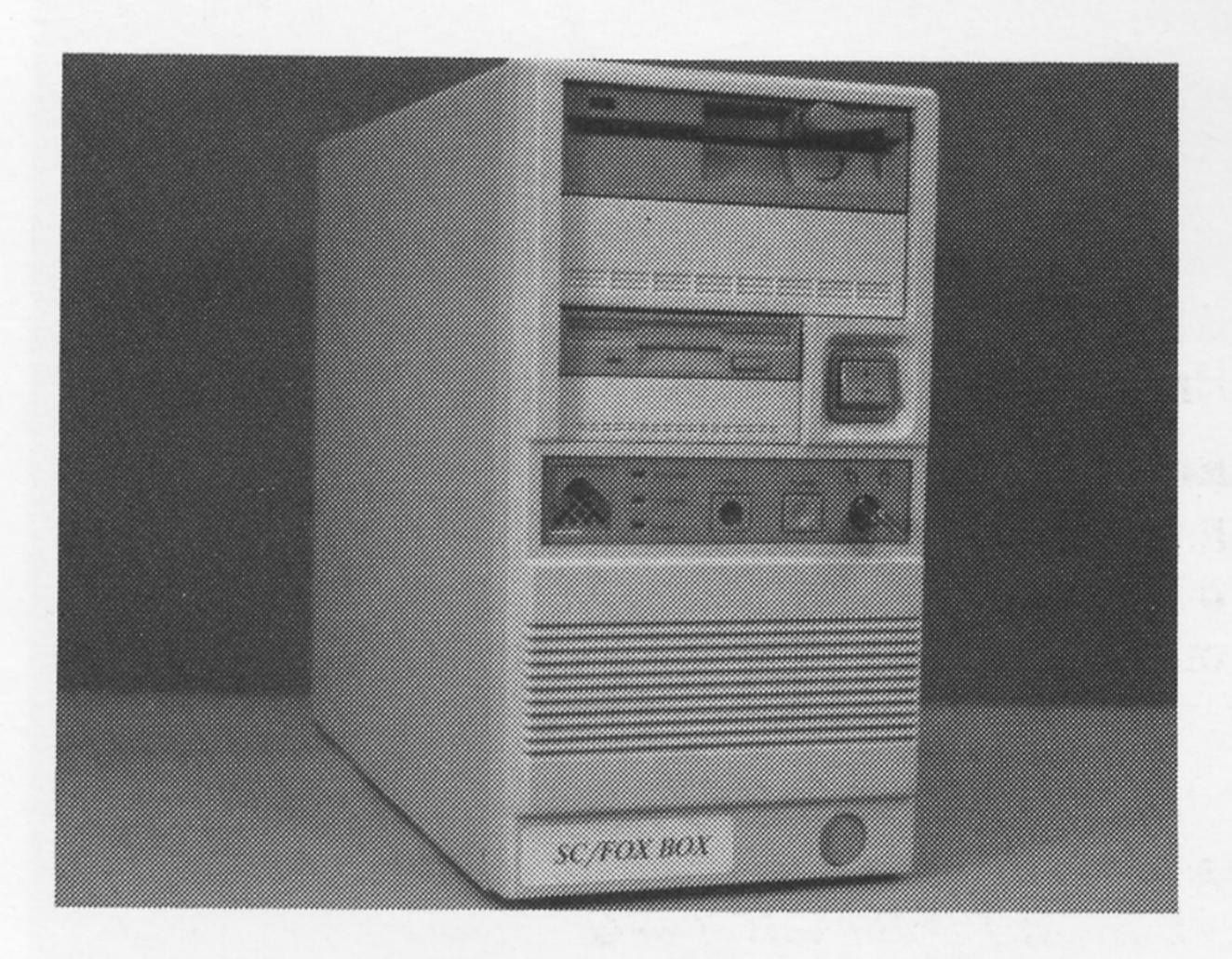

# SC/FOX<sup>tm</sup> BOX Computer System

# The SC/FOX (Forth Optimized eXpress) BOX is a

high-speed stand-alone computer, designed both as a real-time development platform and a system controller for embedded applications. Mounted inside is the SC/FOX Single Board Computer, a small (100x160mm) stand-alone computer that uses the 16-bit RTX 2000 Forth CPU, and the SCSI I/O board. Communication with the SC/FOX BOX takes place across a 56K-baud RS-232 serial port, to either a PC compatible computer or a stand-alone terminal. The SC/FOX BOX boots from its on-board EPROMs, and loads software or data from the SCSI hard disk, floppy drives, or serial port.

# SC/Forth Language

- \* Interactive language, Forth-83 Standard.

- \* Automatic optimization and µcode support.

- \* Time-slice or user-defined multitasking.

- \* Code overlay system and program spawning.

# Mini-Tower Enclosure: 13"x16"x7".

- \* 200-watt power supply.

- \* Two 5¼" half-height bays and three 3½" half-height bays (one for 3½" hard disk).

- \* Optional full-tower enclosure.

- \* Wyse 150 terminal and software.

- \* Custom configurations quoted.

# SC/FOX SBC Single Board Computer

- \* Uses Harris RTX 2000<sup>tm</sup> Forth Chip.

- \* 8, 10, 12, or 14 MHz operation.

- \* 64K to 512K bytes zero-wait state SRAM.

- \* 56K baud serial terminal port.

- \* Centronic parallel printer port.

# SC/FOX SCSI I/O Daughter Board

- \* SCSI port for disk drives, optical drives, etc.

- \* Floppy disk port supports up to 4 disk drives.

- \* 56K baud serial port.

- \* 16-bit bidirectional latching I/O port.

# **External Ports**

- \* 9-pin RS-232 terminal and serial port.

- \* 25-pin Centronic parallel port.

- \* 40-pin bidirectional parallel port.

- \* 50-pin SCSI I/O port.

# Standard Mini-Tower Configuration

- \* 8 MHz SBC with 128K bytes SRAM.

- \* SCSI I/O board with software drivers.

- \* Two 5.25" 1.2M byte floppy drives.

- \* One 40M-byte SCSI hard disk drive.

- \* SC/Forth in on-board shadow EPROM.

- \* Room inside for custom hardware.

Ideal for embedded real-time control, high-speed data acquisition and reduction, image or signal processing, or computation-intense applications. For additional information, please contact us at:

SILICON COMPOSERS INC 208 California Avenue, Palo Alto, CA 94306 (415) 322-8763

### DESIGN TRADEOFFS IN STACK COMPUTERS PHILIP KOOPMAN, JR.

5

When the author started, all he knew was that Forth programs did a *lot* of subroutine calls. Here he describes the discoveries, blunders, and serendipity that led to the WISC and 32-bit RTX processors, including the requirements of a high-speed Forth engine and the motivations underlying Harris' 32-bit architecture.

### SC32: A 32-BIT FORTH ENGINE - JOHN HAYES

10

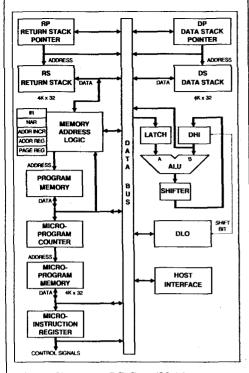

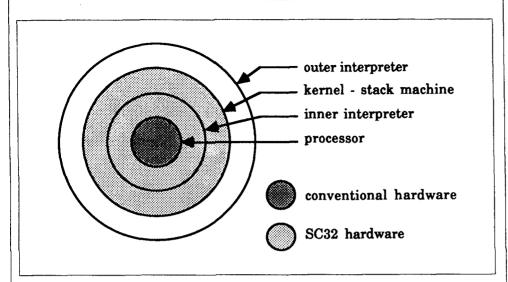

A group at Johns Hopkins University has designed a series of microprocessors that directly execute Forth, to which the SC32 is the latest entry. Three key aspects are described: elimination of run-time interpretation, an instruction set optimized for Forth, and an internal data path that supports stack-based programming.

### PHASE ANGLE DIFFERENCE ANALYZER - C.H. TING

15

The Phase Angle Difference Analyzer determines the delay and phase difference between two simultaneous analog signals. The signals are digitized, then the results are analyzed by an NC4000 microprocessor. The system samples at a rate of 400 KHz, a speed unattainable by most commercial CPUs.

### ANS FORTH: HARDWARE INDEPENDENCE - JOHN R. HAYES

23

One of Forth's strengths is its usefulness in "strange" environments, but the Forth-83 Standard mandates byte-addressed memory, 16-bit operations, and two's-complement number representation. Yet, when programming for profit, a portable program has a larger potential market than a non-portable program.

### FORML CONFERENCE 1989 - PETER MIDNIGHT

27

Foremost Forth programmers from around the world ostensibly gathered to discuss object-oriented programming but, as the author points out, the real purpose of FORML is to bring together serious Forth users and to propagate their enthusiasm, ideas, and information.

### SORT CONTEST RESULTS - DENNIS RUFFER

29

Several months ago, these pages announced a sort contest sponsored by this GEnie Sysop. Now the results are in, and we have a winner... Also included is code and commentary from Forth-wizardly Wil Baden.

Editorial

4

Best of GEnie

35

Advertisers Index

9

FIG Chapters 40, 42-43

# **EDITORIAL**

### **Forth Hardware**

This issue contains the top three articles selected from those we received in response to our call for articles about Forth hardware. It was a successful experiment, in my jaded editorial eyes, because it brought us a number of very good manuscripts (only three of which are presented in this issue—we will publish others, with their authors' permission, in upcoming issues). There was an interesting split decision in the judging, calling for editorial arbitration, but Phil Koopman's "Design Tradeoffs in Stack Computers" received a unanimous vote for first place. Second place went to John Hayes for "The SC-32: a 32-Bit Forth Engine," while third place went to Dr. C.H. Ting's "Phase Angle Difference Analyzer." Cash awards will be sent to those three authors in recognition of their contributions. We are honored and pleased to bring you their work.

Times have changed since Glen Haydon and Chuck Moore closeted themselves in Glen's computer-riddled crow's nest, densely wire-wrapped boards lying like disemboweled mazes atop the gurneys they used for workbenches. Chuck left to develop what would become the NC2000 for Novix (a device that will probably be remembered only as the first real Forth chip). Well, the hardware bug bit some of the best minds in the Forth world, and it bit them hard. Perhaps they sensed, as Jack Woehr suggested in the last issue, that Forth as we have known it all these years is—at its most metaphysical roots—an evolving description of an ultra-efficient microprocessor architecture. Or perhaps it was just that Forth's way of seducing us into hardware intimacy led us to believe we could do anything.

In any case, soon we had a selection of interesting devices to tinker with. Industri-

ous efforts (some realized and some not) sprang out of small shops and universities, and there were Zilog's Super8 and Rockwell's R65F11. These actually became bread-and-butter hardware for some Forth programmers.

Re-enter Glen Haydon, who had teamed up with Phil Koopman, Jr. Soon the Haydons' loft was streaming out schematics, and the two of them were selling wirewrap kits and PC boards as the promising WISC (i.e., writeable instruction set computer) CPU/16 and CPU/32. These were stack-based devices whose native instruction sets could be changed about as easily as a Forth definition, and they blazed right along at fine speed. Phil also dove into a doctoral program; his résumé must have left the entrance examiners a bit breathless, unless they are accustomed to candidates who have already implemented working examples of a promising, untried microprocessor architecture. Much of his interesting research has been published as Stack Computers, The New Wave.

The kicker is that the CPU/16 and /32 drew the attention of Harris Semiconductor. Harris negotiated for the rights to develop this technology, and since then have invested considerably in its success. They incorporated the WISC concepts in their standard cell library and produced the RTX 4000 microprocessor; the RTX 2000 is their Novix successor.

This string of developments, which continues to unfold, offers hope for the future employment of Forth programmers: if any large chip maker manages to pinpoint the conjunction of Forth's strengths and the market's evolving needs, there could be a decided upswing for hardware experts, systems vendors, developers, consultants, and plain-old programmers. Already,

(Continued on page 34.)

### **Forth Dimensions**

Published by the

Forth Interest Group

Volume XI, Number 6

March/April 1990

Editor

Marlin Ouverson

Advertising Manager

Kent Safford

Design and Production

Berglund Graphics

Forth Dimensions welcomes editorial material, letters to the editor, and comments from its readers. No responsibility is assumed for accuracy of submissions.

Subscription to Forth Dimensions is included with membership in the Forth Interest Group at \$30 per year (\$42 overseas air). For membership, change of address, and to submit items for publication, the address is: Forth Interest Group, P.O. Box 8231, San Jose, California 95155. Administrative offices and advertising sales: 408-277-0668.

Copyright © 1990 by Forth Interest Group, Inc. The material contained in this periodical (but not the code) is copyrighted by the individual authors of the articles and by Forth Interest Group, Inc., respectively. Any reproduction or use of this periodical as it is compiled or the articles, except reproductions for non-commercial purposes, without the written permission of Forth Interest Group, Inc. is a violation of the Copyright Laws. Any code bearing a copyright notice, however, can be used only with permission of the copyright holder.

### **About the Forth Interest Group**

The Forth Interest Group is the association of programmers, managers, and engineers who create practical, Forth-based solutions to real-world needs. Many research hardware and software designs that will advance the general state of the art. FIG provides a climate of intellectual exchange and benefits intended to assist each of its members. Publications, conferences, seminars, telecommunications, and area chapter meetings are among its activities.

"Forth Dimensions (ISSN 0884-0822) is published bimonthly for \$24/36 per year by the Forth Interest Group, 1330 S. Bascom Ave., Suite D, San Jose, CA 95128. Second-class postage paid at San Jose, CA. POSTMASTER: Send address changes to Forth Dimensions, P.O. Box 8231, San Jose, CA 95155."

# DESIGN TRADEOFFS IN STACK COMPUTERS

### A PERSONAL EXPERIENCE

PHILIP KOOPMAN, JR. - WEXFORD, PENNSYLVANIA

When I started designing stack processors for WISC Technologies in 1985, little had been published about the architectural requirements of Forth engines. A substantial amount of architectural measurement had been performed on previous stack-based processors (in particular the Xerox Mesa architecture), but the behavior of single-stack processors for executing conventional languages is not representative of the types of things Forth processors do. When I started, all I knew was that Forth programs did a lot of subroutine calls, but beyond that I was groping in the dark. Here I hope to describe some of the history behind the development of the WISC and 32-bit RTX processors in terms of discoveries, blunders, and serendipity. Along the way, I will talk about the various requirements for implementing a high-speed Forth engine, and will describe the motivations underlying the design of Harris' 32-bit RTX architecture.

### THE HARDWARE-FRENZY PHASE

The first phase of my continuing journey to stack-computer enlightenment was characterized by a frenzy of designing, building, debugging, and programming Forth hardware.

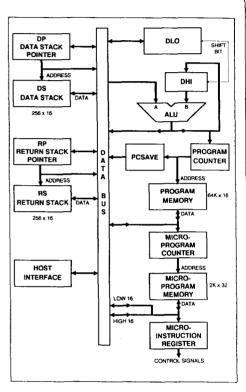

### The WISC CPU/16

The WISC CPU/16 was my first stack computer design (and, for that matter, my first computer design of any type). The "WISC" stands for Writable Instruction Stack Computer. It was implemented entirely in 74LSxxx series TTL components, wire-wrapped on a single IBM-PC plug-in board. We produced a printed circuit board version once the design was shaken out. The design decisions for the CPU/16 were made in favor of simple and inexpensive

prototyping first and foremost. This led to the decision to use a microcoded design, with RAM chips for a writable control store instead of a hardwired design.<sup>1</sup> A block diagram of the CPU/16 is shown in Figure One.

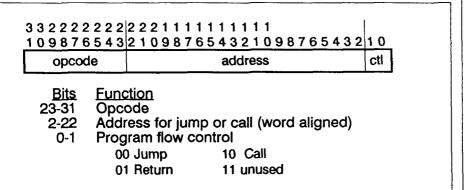

The design had 256 elements for each stack, and 256 opcodes with eight possible micro-instructions per opcode. Most instructions took three micro-cycles to execute, with subroutine calls and returns tying up the data bus to the exclusion of other operations. Figure Two shows the two instruction types supported: subroutine call and opcode. Thus, the importance of Forth's subroutine call was incorporated, but the rest of the design was dictated primarily by the constraints of fitting everything onto a single board while still using standard TTL components.

# The RISC vs. CISC battle was about to take a new turn...

The Novix NC4000 chip had been introduced shortly before the WISC CPU/16 was built. A principle difference between the two designs (other than the fact that the Novix was a single chip compared to the CPU/16 discrete implementation) was that the Novix was a hardwired processor, while the CPU/16 was microcoded. The simplistic microcode implementation techniques used on the CPU/16 caused it to take an

Figure One. WISC CPU/16 block diagram.

average of three micro-instructions for each opcode (at a cost of three clock cycles). At similar clock speeds (which translated into similar program memory speeds), one would have expected the NC4000 to outperform the CPU/16 by a factor of three to one.

But that didn't happen. Instead, the 4.77 MHz CPU/16 was much slower than a 5 MHz NC4000 on programs that used simple operations, but competitive (although, probably, not quite as fast) on programs that used more complex operations. This was because complex operations,

<sup>1.</sup> This decision was perhaps influenced by the fact that I did not possess an EPROM programmer, and that available programmable logic for use in synthesizing random logic was very modest in capabilities—and I didn't have a programmer for that either.

### 1 1 1 1 1 1 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 address

Bits Function

0-15 Subroutine address

(bits 8-15 of the address must not all be 1)

Bits Function

8-15 All 1, specifying an operation instruction

0-7 Opcode

Figure Two. CPU/16 instruction formats.

Figure Three. CPU/32 instruction format.

such as double-precision math and multielement stack manipulations, were implemented in microcode in fewer clock cycles than the equivalent sequences in NC4000 assembly language. The execution speed for a mix of Forth primitives was just under one million typical Forth operations per second (including complicated operations such as multiply and double-precision math in a typical instruction mix).

As a result of my CPU/16 experience, I think microcoded techniques are inappropriate for a 16-bit Forth processor in most cases. Primarily, this is because the requirements for 32-bit wide microcode cause a single-chip implementation to be too large to be competitive with a hardwired approach. Also, the use of a microcoded approach does not provide many additional benefits when the processor is restricted to

a 16-bit instruction format. However, the experience showed that something interesting was possible—microcoded machines could, perhaps, be competitive with hardwired machines with similar functions. This was because flexibility of operation and a high semantic content in each instruction could make up for a lack of raw speed. In other words, the RISC vs. CISC battle was about to take a new turn in the arena of stack computers.

### The Monster/32

WISC Technologies produced a single prototype of a 32-bit computer that was seen by a very few people at the 1986 Rochester Forth Conference. In his book *The Mythical Man-Month* (Addison-Wesley, 1982), Fred Brooks describes what he calls the "second system syn-

drome." In this syndrome, the designer of a system saves up scores of neat ideas that can't be implemented in the first system because of time and money constraints. When the designer gets another crack at a similar problem (the second system), all these ideas are thrown in, usually with disastrous results.

The Monster/32 was my second system. The only truly good idea that was included was the decision to make it a 32-bit machine. Some of the ideas were reasonably good, but poorly executed. One idea was the inclusion of extra registers around the ALU. This eliminated congestion caused by having to save and restore the top-of-stack register when using the ALU for other calculations. Another idea was the addition of separate hardware to increment subroutine return addresses independent of the ALU.

The worst ideas had to do with the micro-instruction format and the use of multiple counters for addressing program memory. The 64-bit micro-instructions had a large number of interesting features, including the capability to specify a variable length for each micro-cycle. None of these features turned out to be very useful. The complexity of the micro-instruction format did result in almost impenetrable micro-code that was very difficult to write and debug.

The Monster/32 was constructed using eight wire-wrapped boards in an S-100 card cage (but without using the S-100 bus in the usual manner). The wire-wrapping exercise itself taught me an important lesson about the value of simplicity, and wore out my first electric wire-wrap gun.2 The system was eventually operational for a period of two weeks, and successfully ran a Forth system. The folks who saw it operate at the Rochester Forth conference never did ask why the attachment cable to the IBM PC host was only a foot long. There was an incredible noise problem in the host interface, and any longer cable wouldn't work reliably.

It became clear that, for a number of reasons, my first 32-bit design was a flop. Fred Brooks, again in *The Mythical Man-Month*, asserts that you should always be prepared to "throw one away." So we did.

<sup>2.</sup> Based on this experience, I rate battery-powered wire-wrap guns at about two miles of wire per gun.

Figure Four. WISC CPU/32 block diagram.

### The CPU/32

I began to distill the Monster/32 experience, and to decide what formed the true essence of an efficient WISC system. The CPU/16 had been arbitrarily constrained to simplicity, whereas the Monster/32 had been allowed to grow almost limitlessly. While there were a few good ideas to be salvaged, overall my immensely complex 32-bit design was a waste of good silicon. I began to see what I had missed in the realm of hardware design, despite my extensive experience with Forth: within limits, simpler is better.

At the same time, I began to combine several ideas that had been collecting in the back of my mind. One of them was that CPU cycle times can be made much faster than affordable memory speeds. Another was that taking advantage of concurrency in operations is a traditional way of speeding up computers that I had not exploited very well in previous designs. The last major idea was that, since microcoded stack machines only need eight or nine bits to specify an opcode, much of my 32-bit instruction memory was being wasted as unused bits in opcode-type instructions.

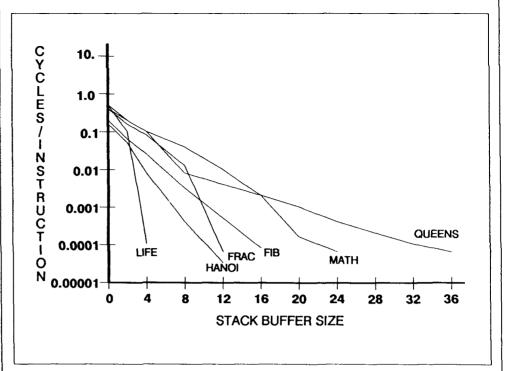

Figure Five. Return stack spilling overhead vs. stack buffer size.

The answer to all my collected concerns hit like a bolt of lightning one day.3 There were enough bits left over in an opcode instruction to also hold a large address, so why not make every instruction have both an opcode and a subroutine call? This had the effect of reducing program size, as well as providing for simultaneous operation of subroutine calls and opcodes. Thus, the resulting machine allowed control flow (subroutine calls and returns) to proceed in parallel with data manipulations (data stack operations), allowing two separate operations to be accomplished on each instruction. In other words, it offered the ideal situation for a Forth programmer: subroutine calls for free. Of course, in order to have a complete set of machine operations, a subroutine return format was required, which also combined an opcode with the return operation.

Not every instruction was a subroutine call or return, so there was a need for an instruction that incremented the program counter as well. In my quest to simplify the hardware, I made another discovery: the program counter was unnecessary. By using a jump instruction format instead of an increment-PC instruction format, I could have every instruction point to the next instruction to be executed (even if it was just the next sequential instruction). This

reused the logic that performs subroutine calls, with a modification to suppress the push of the return address onto the return stack. The instruction format of the CPU/32 is shown in Figure Three.

Other enhancements to the CPU/32, based on experiences with the Monster/32 and the limitations of the CPU/16, included using a latch between the bus and the ALU to facilitate single-cycle exchange of data between the DHI register and the Data Stack. The microcode format was trimmed back to 32 bits, which makes microcode simple enough to be easily comprehensible, and saves a large amount of memory space. A block diagram of the CPU/32 is shown in Figure Four.

Another important insight in the design of the CPU/32 was the balance achieved between program memory speed and processor speed. RISC processors strive to execute one instruction per clock cycle. That implies that memory must be cycled as quickly as the clock in order to provide a steady stream of instructions. In a simple and streamlined processor, that means that programs must reside in fast memory. Usually, the required memory chips are so expensive that even high-end RISC systems must use them sparingly as cache memories. Many Forth applications have traditionally been in the areas of real-time

<sup>3.</sup> I don't remember just how the idea came to me. My best ideas usually come during my morning shower. However I was not electrocuted, so this one probably did not.

control. Many real-time control applications cannot afford the unpredictability of cache memory. Many others can't afford the cost of even a single bank of fast memory chips for any purpose. So, taking advantage of the fact that a microcoded machine can have a higher instruction semantic content (i.e., it can accomplish more work per instruction), I designed the CPU/ 32 to execute an instruction every two micro-cycles, with each memory bus cycle taking two clock cycles. Assuming that both micro-cycles of every instruction are well employed, this allows twice the processing power for a given memory speed than an approach of one instruction per clock cycle.

The CPU/32 was originally built on reused S-100 boards from the Monster/32, with 74ALSxxx logic and some 74Fxxx logic for speed-critical sections. The use of "F" logic caused enough noise problems that the wire-wrapped version never ran at speed, so we produced a printed circuit board version before debugging was completed. This five-board version eventually ran at a 6 MHz micro-cycle rate, and executed approximately three million Forth operations per second.

### The RTX 32P

The finished CPU/32 was demonstrated at the 1987 Rochester Forth Conference, At that conference, Harris Semiconductor was promoting its RTX 2000 processor, a redesign of the NC4000. They were intrigued by the possibilities for the CPU/32 as a 32bit member of the RTX family. So, in July of 1987, I visited Melbourne Florida and transferred the schematics of the CPU/32 into their standard cell design system. In 31 days, the design was entered and verified with the help of one Harris engineer.4 The product of this effort was, in January of 1988, an implementation that was functionally identical to the three printed circuit boards of the CPU/32 core processor, reduced to two chips operating at an 8.3 MHz micro-cycle rate. The two chips were the data chip (with the ALU, data stack, and half the microcode memory) and the control chip (with the memory addressing logic, the return stack, and the other half of the microcode memory).

The reason for a two-chip set instead of

a single-chip processor implementation was to allow maximum flexibility with the finished system. 2K words of microcode memory were included on-chip, since 256 opcodes seemed to be more than I could possibly use.5 When asked how big the stacks should be, I replied, "Gee, how much will you give me?" So, the chips ended up with 512 elements by 32 bits each for data and return stacks. This resulted in three things: it allowed Harris to make the biggest chip they have ever attempted, it made for a poor yield, and it produced chips which have logic on one quarter and memory in the other three. But, all these results were in keeping with the experimental nature of the project.

### THE ANALYSIS PHASE

After the successful production of the CPU/32, I began to define and build a commercial version of the architecture for inclusion in the RTX product family. This exercise involved optimizing the architecture to fit the design constraints of CMOS chip technology as well as evolving the architecture to improve performance and better address the needs of the marketplace.

In the summer of 1987, I foolishly agreed to simultaneously refine the architecture for Harris and write a book about stack computer architecture. I did survive the summer, and found that the synergy between the two tasks was amazing. The book required me to think about measuring and describing the essence of stack machines. The design task required me to think about efficiency and architectural refinement. By the end of the summer, I had reached a number of conclusions about tradeoffs in stack machine design.

### Stack Size

One of the big unknowns in producing the RTX 32P was how big to make the stacks. Before, I had been limited either by the need to keep chip count low or by standard high-speed memory chip sizes. On the RTX 32P, I guessed at 512 stack elements.

I guessed wrong. Simulations of several Forth programs show that many programs never used more than four or five stack elements. Of those that used more stack elements, all showed a small variability in stack size across reasonably large periods of time. In order to reduce hardware costs, it is advantageous to exploit this behavior and reduce on-chip stack sizes to the minimum possible.

An interesting line of thought to pursue is to assume that on-chip stacks are so expensive that they will be smaller than required. Also assume that there is some mechanism (say, a finite state machine that monitors stack overflows and underflows) that will copy elements to and from memory as required. The question to ask, then, is how much does this copying cost in terms of program performance degradation? Figure Five shows the results of a simulation for the return stack on a number of programs. The vertical axis indicates the amortized costs of stack spills in terms of wasted memory cycles per instruction executed in the course of the program. Notice that this axis has a logarithmic scale. The horizontal axis specifies the size of the on-chip stack buffer. The amazing thing is that, for a stack size of 16 elements, the cost is less than one percent. For a stack size of 16 to 32 elements, the cost reduces to essentially zero. Data stack behavior is similar.

The right answer, then, to how big stacks should be is 16 or 32 elements, no more. In the case of a multitasking environment, it is advantageous to have a partitioned stack that allocates 16 or 32 stack elements for each task in order to eliminate context-switching overhead.

### Hardwired vs. Microcoded Performance

With the design of the RTX 32P, the hardwired control vs. microcoded control issue became ripe for detailed study. The RTX 2000 and the RTX 32P represent two processors designed to accomplish similar tasks using similar technology. One is hardwired, the other microcoded. The question is, which is faster?

I collected statistics on instruction execution frequency for Forth programs. But, I didn't simply gather numbers for the obvious primitives such as DUP, +, and SWAP. Instead, I took an IBM PC Forth compiler that was optimized to the point that anything worth speeding up was written in assembly language. This became my set of Forth "primitives"; that is, the basic building blocks used by real Forth code in real programs. Not surprisingly, these primitives included many double-precision operations (including "2-type" stack opera-

<sup>4.</sup> That includes the weekend I took off to visit Walt Disney World.

<sup>5.</sup> Of course this means that they were completely filled with mostly worthless junk almost immediately.

tions), and slow instructions such as multiply and divide. After I had measured the instruction execution frequencies for several programs, I multiplied the frequency times the number of clock cycles required for each of the RTX 2000 and RTX 32P processors. I assumed that RTX 2000 programs were operating on 16-bit data, and that RTX 32P programs were operating on 32-bit data. The result was surprising.

Despite the fact that most instructions on the RTX 2000 execute in a single clock cycle and that all instructions on the RTX 32P execute in two or more clock cycles, the RTX 32P required only ten percent more clock cycles than the RTX 2000 to do the same amount of work. In other words, clock-for-clock, the two processors did about the same amount of work. Part of the reason for the RTX 32P's good performance was the fact that its microcoded opcodes mapped well onto the high-level Forth operations used in real programs. Another part of the reason was that many of the subroutine calls counted as instructions, but were executed "for free" by the RTX 32P when combined with opcodes in the same machine instruction. Note that, although the program execution speed is similar, the RTX 32P accomplishes the same amount of work in half the memory accesses as the RTX 2000, since it accesses memory every two clock cycles. This difference allows it to use much slower memory for comparable processing speeds.

The result of this comparison is that it is not clear that the RISC approach of hardwired instructions and single-clock-cycle execution offers a compelling benefit over microcoded designs in terms of program execution speed for stack machines. This means that designing a 32-bit processor with hardwired control may result in suboptimal use of available memory bandwidth. For reasons previously stated, this should not be interpreted as meaning that 16-bit Forth chips should be designed with microcoded control—the area costs are just too high, and the lack of bits in the instruction format to support simultaneous opcode and subroutine call execution makes the potential payoff too low.

### C—The Realities of the Marketplace

Forth is Good. But, Forth doesn't always Sell. The fact is, C is becoming the language of choice in many application areas, including real-time control. Also,

architectural features required to support C go a long way towards supporting Ada for the military market. So, the RTX family is migrating to a position in which C is the primary language for many users. Forth then becomes the "assembly language" for the system, used for optimizing critical routines.

Aside from minor quirks of C (such as signed and unsigned characters, requiring optional signed byte extension on byte fetches), the only important C structure that is incompatible with Forth-based stack machines is the stack frame. C semantics assume that anything in the stack frame is addressable as a normal memory element. Furthermore, C stack frames grow too big to fit into any reasonably sized on-chip stack buffer. So, a stack processor must have some efficient method of supporting a stack frame. At a minimum, this means having a dedicated frame pointer on-chip, as well as the capability for using framepointer-plus-offset addressing. The RTX 2000 design incorporated a movable User Area pointer that can fulfill this requirement (an improvement over the NC4000, which had a fixed User Area location). The RTX 32P did not have this capability, but you can be assured that the commercial 32bit RTX chip will.

For Forth users, the frame pointer can provide unexpected benefits. Many Forth programmers have advocated the use of local variables of some sort as a way of improving code organization and readability. A frame pointer mechanism makes an ideal implementation vehicle for a local variable stack, as well as providing a clean interface between C procedures and Forth subroutines.

### **Conclusions**

I've described some of the history behind the sequence of processors leading up to the 32-bit RTX chip now in development. Along the way, I've tried to give some insight into why the processors have been designed the way they have, and into stack machine design issues in general. While the information has been presented as a personal history, it should provide some idea of the essential elements of designing stack computers.

In the real world, design of a good architecture is seldom done entirely through the sole use of wisdom and knowledge, and is never done right on the first try. Happenstance, and the background and education of the designer have much to do with the process. More important than the ability to get it right the first time is the ability to recognize mistakes, try new ideas, and retain the best of the old while incorporating the best of the new.

I would like to take this opportunity to acknowledge the involvement of two people without whom this history could not have taken place. Glen Haydon provided insight, encouragement, and financial support for the WISC Technologies processors. Dave Williams has been personally responsible for the acceptance and survival of the RTX 32-bit technology at Harris Semiconductor.

Philip Koopman Jr. is a senior scientist at Harris Semiconductor.

### **ADVERTISERS INDEX**

| Forth Interest Group                    | 44    |

|-----------------------------------------|-------|

| Harvard Softworks                       | 16    |

| Inner Access                            | 18    |

| Institute for Applied Forth Research    | 38    |

| Journal of Forth Application & Research | 6, 37 |

| Laboratory Microsystems                 | 18    |

| Miller Microcomputer Services           | 24    |

| Next Generation Systems                 | 14    |

| Silicon Composers                       | 2, 26 |

### SC32: A 32-BIT FORTH ENGINE

JOHN HAYES - LAUREL, MARYLAND

Over a period of several years, a group of us at the Johns Hopkins University Applied Physics Laboratory have designed a series of microprocessors that directly execute the Forth programming language. The SC32 is the third in the series.

Interpreted languages have a big advantage over compiled languages, in their shorter software development cycles and their ability to interactively test and debug programs. This is especially true with Forth, whose simple syntax allows it to be extended in application-unique ways. Unfortunately, the performance of Forth on conventional computers suffers when compared to compiled languages because of the need for run-time interpretation. Forth-oriented processor chips, by treating Forth as object code, eliminate run-time interpretation. Consequently, interactive Forth programs running on the SC32 execute just as fast as equivalent compiled programs on conventional microprocessors.

All of the SC32's internal and external data paths are 32 bits wide. The chip has an external 32-bit address bus and 32-bit data bus. 16-bit processors will be useful in many applications for years to come. However, once the size of a program or its data exceeds the memory addressable by a 16-bit processor, the bank switching and segmentation schemes that must be resorted to hurt system performance. The flat, linear address space of a 32-bit processor provides the most convenient programming model for large applications.

### **Forth Direct Execution**

The SC32 directly executes the Forth programming language. From this description, you might think that the chip reads in

Forth source code and executes it. However, the reality is less exotic and more subtle. Three aspects of the SC32 make it a Forth direct-execution engine: elimination of runtime interpretation, an instruction set optimized for Forth, and an internal processor data path designed to support Forth stack-based programming. Each of these points is discussed in the sections that follow.

# Most Forth primitives are implemented with one instruction.

### Eliminating the Inner Interpreter

Forth is implemented on traditional processors using the virtual machine approach shown in Figure One. Because of the mismatch between Forth's stack model and the native processor, a layer of run-time interpretation is necessary. A tiny assembly language program called the inner (or address) interpreter is written for the bare processor. Forth's primitive stack operators, also written in assembly language, are implemented in the kernel layer. The top layer of a Forth system, the interactive outer interpreter is written in Forth. The SC32 processor implements the inner interpreter and kernel layers in hardware, eliminating run-time interpretation. This means that Forth programs running on the SC32 execute as fast as equivalent compiled programs while retaining Forth's interactive environment.

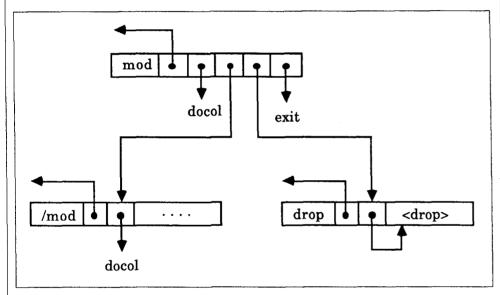

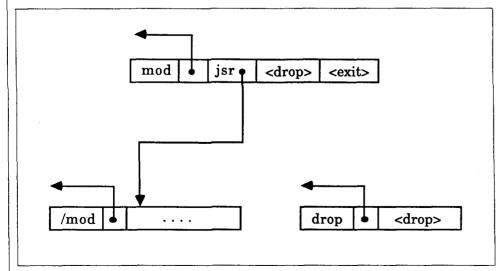

The inner interpreter in traditional Forth systems uses a technique called threaded code [Rit80]. Figure Two shows how the Forth program:

: mod /mod drop ;

is compiled on an indirect-threaded code system. /MOD has been previously defined using: (colon). In the body of MOD's definition, /MOD and DROP are represented as pointers (threads) to their respective definitions. DROP is a primitive and its definition is in assembly language. The definition of /MOD, another colon definition, consists of threads to its constituents.

When MOD is executed, the inner interpreter traces through the list of threads, nesting down when necessary, until a primitive word defined in assembly language is found. Control is then transferred to the primitive. In Forth systems implemented on traditional processors, 35–50% of the system's time is consumed by the inner interpreter.

The SC32 eliminates this run-time overhead by eliminating the inner interpreter. Figure Three shows the MOD example compiled for the SC32. Instead of a pointer to DROP, the actual object code for DROP appears within MOD's definition. The pointer to /MOD is replaced with a subroutine call to /MOD. At run time, a list of SC32 instructions is traced, instead of a list of pointers. The inner interpreter has become the fetch-execute cycle of the processor.

Readers familiar with advanced Forth implementation techniques will realize that the scheme described above is subroutine threaded with in-line code expansion. Theoretically, nothing precludes using this technique on conventional processors. However, the mismatch between Forth and typical instruction sets would cause compiled Forth programs to become much larger. For example, if several instructions are needed to implement DUP on a given

Figure One. The Forth virtual machine.

Figure Two. Indirect-threaded code.

Figure Three. Direct execution.

processor, the resulting object code could be significantly bigger than the size of a thread. The instruction set of the SC32 has been designed so that almost all Forth primitives are implemented with one instruction. This is the subject of the next section.

### **Instruction Set**

The SC32 instruction set was designed specifically to support the Forth programming language. There is a one-to-one mapping between most Forth primitives (DUP, +, DROP, etc.) and SC32 instructions. All of the instructions execute in one machine clock cycle, with the exception of load-from-memory and store-to-memory, which take two cycles. Consequently, a complete Forth primitive is executed almost every clock cycle.

All SC32 instructions are 32 bits wide. Having 32 bits to represent instructions allows a chip designer to create a more regular instruction set with less instruction decoding circuitry needed on chip. Less decoding logic allows the chip's clock rate to be increased, reducing the time needed to execute an instruction. The instructions come in three categories: control flow, loads/stores, and arithmetic operations. Table One shows each instruction type available within a given category. There are a total of eight instruction types, with the three most significant bits of the instruction determining its type.

The notation used to describe the instructions in Table One is unusual. Traditional assembly languages, consisting of an operation followed by operands, are inadequate for describing the SC32's instruction set. Instead, a register transfer notation is used in Table One and throughout this article.

There are three control flow instructions: subroutine call, branch, and conditional branch. These instructions all contain an embedded destination address. Measurements show that a single-cycle subroutine call is the most important ingredient of a Forth engine. Calling a colondefined word from within another colon word is the most frequently executed operation in Forth programs. The bit-level instruction encoding of the call instruction was chosen so that the processor interprets any 32-bit pointer (thread) into the low words of memory as a subroutine call.

Fast branch instructions are important too. A single-bit condition code flag deter-

mines whether or not the conditional branch is taken. The flag must be set by an earlier instruction.

The load/store category of instructions consists of load-from-memory, store-tomemory, load-address-low, and load-address-high. In these instructions (and in the micro-instruction described below), R1 and R2 are operand selectors. Possible operands include the top four locations on Forth's parameter stack, the top four return stack locations, and miscellaneous registers. The load-from-memory instruction takes the operand specified by R1, adds a 16-bit Offset value to form a memory address, fetches a value from memory, and places it where indicated by R2. Store-tomemory is similar, but the R2 operand is stored at the computed memory address. These two instructions take two clock cycles to execute. In the load-address-low instruction, the address computation is performed as described above. However, instead of fetching from memory, the address is put in R2. The load-address-high is similar, but the Offset value is shifted left sixteen bits before being added to R1. The load address instructions execute in one clock.

The micro-instruction (so called because of its similarity to conventional microcode) performs arithmetic, logic, and shift functions. One ALU operand is selected by R1 and the other operand is always on the top of the parameter stack. The ALU result is stored in R2. Much detail about the micro-instruction has been suppressed in Table One. The ALUop control field actually has two formats, one for controlling shift operations and the other for controlling arithmetic operations. The arithmetic format has six subfields for selecting the arithmetic operation, the source of the carry input, and the result to be loaded in the condition code flag. The shift format is similar, except that the arithmetic operation subfield is replaced by four shift control subfields.

Micro and load/store category instructions also have the ability to control Forth's stacks and select the source of the next instruction using the *Stack* and *Next* fields. *Stack* can specify that any combination of pushing and/or popping the parameter and return stacks should occur in parallel with the execution of the instruction. *Next* selects either the program counter (PC) or the top of the return stack (TOR) as the source address of the next instruction. Usually, the

PC provides the address. However, if TOR is specified in *Next* and the return stack is popped, a return-from-subroutine is done concurrently with the execution of the current instruction. In other words, a subroutine return occurs in zero time. (Note that the similar Novix return bit always popped the return stack [Gol85].)

There are a number of programming tricks that are useful on the SC32 and that help in the implementation of Forth. The single addressing mode, register indirect plus offset, is more powerful than it appears. This simple addressing mode subsumes the functions of several other modes. For example, a register indirect mode results from setting the offset to zero. The SC32 has an internal register that always returns the value zero when read. This allows the construction of an absolute addressing mode by adding the offset to the zero register. The offset becomes an absolute address. More complex addressing modes can be constructed using more than one instruction.

The load address instructions also provide some tricks. Programmers familiar with conventional instruction sets might have been surprised by the absence of a move instruction in Table One. Adding a zero offset to the R1 operand in a load address instruction is equivalent to moving R1 into R2. A move immediate instruction that loads a literal value into R2 can be produced by setting R1 to the zero register. The result is that the offset is loaded into R2. Any 16-bit literal can be produced in one clock cycle using this trick. Any 32-bit literal can be constructed in two clocks using a load-address-high followed by a load-address-low.

### **Data Path**

The data path of a processor is the organization and connectivity of internal resources such as registers and ALUs. The data path, along with some control logic, implements the processor's instruction set. Several elements of the SC32 data path (such as the zero register and condition code flag) have already been mentioned. However, the most important features of the data path are two stack caches, one for the parameter stack and one for the return stack. The stack caches are key to executing one Forth primitive every cycle. The SC32 stack caching algorithm guarantees that the top four values of both stacks are always present in the chip. Consequently, Forth primitives always find their operands on chip and never need extra memory cycles to fetch them.

A stack cache is implemented as a sixteen-word circular buffer. As Forth primitives push or pop words from the stack, the words are added to or removed from the buffer. When the buffer fills, hardware intervenes and inserts two cycles to write a word from the buffer into external memory. When the buffer is almost empty, hardware again intervenes to read a word from external memory back into the buffer. To use the stack caches, the programmer loads a register with the address of the external overflow region. Subsequently, the operation of the stack cache is completely transparent and gives the programmer the illusion of arbitrarily large on-chip stacks.

The concept of a stack cache will probably be new to most readers. Once the idea sinks in, you might wonder how well it performs. Nothing is free, and the extra cycles added on buffer overflow and underflow will slow down a running program. However, measurements show that this "slow down" is less than one percent for typical Forth programs [Hay88]. The depth of the stack oscillates around an average value for long periods of time. The cache attempts to adjust itself so that the buffer is centered on the average depth and captures as large a range of depth variations as possible.

### Forth on the SC32

Now that we've examined the three elements of the SC32 direct execution engine, it's time to see how Forth is implemented on the processor. Table Two shows some representative Forth primitives implemented with the SC32 instruction set. The stack operations that push or pop the parameter stack are denoted by  $\sqrt{P}$  and  $\sqrt{P}$ .

DUP is implemented with a load-ad-dress-low instruction. The value on the top of the parameter stack (TOS) is read into the ALU and zero is added to it. In the meantime, the parameter stack is pushed, allocating a new top-of-stack slot. Then the ALU result is written into the slot. The entire operation takes one clock cycle. Notice that in Table Two, operand selectors to the right of the arrow refer to the state of the stack after the push or pop has occurred. Thus, the two uses of TOS in DUP refer to two different storage locations.

A slew of Forth data movement primitives can be built with the load-address-low

| ontrol flow | Type:3                       | Type:3 Address:29              |                                       |                                                                     |                                                                                                               |           |  |  |

|-------------|------------------------------|--------------------------------|---------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------|--|--|

|             | call<br>branch<br>conditions | al branch                      |                                       |                                                                     |                                                                                                               |           |  |  |

| ad/store    | Type:3                       | Next:1                         | R1:4                                  | R2:4                                                                | Stack:4                                                                                                       | Offset:16 |  |  |

|             |                              | ess low (lal)<br>ess high (lal |                                       | *(R <sub>1</sub> + 0<br>*(R <sub>1</sub> + 0<br>R <sub>1</sub> + Of | Offset) $\rightarrow R_2$ Offset) $\leftarrow R_2$ fset $\rightarrow R_2$ fset $\cdot 2^{16} \rightarrow R_2$ | :         |  |  |

| nicro       | Type:3                       | Next:1                         | R1:4                                  | R2:4                                                                | Stack:4                                                                                                       | ALUop:16  |  |  |

| micro       |                              | <u> </u>                       | · · · · · · · · · · · · · · · · · · · | R. ALI                                                              | Jop TOS → R                                                                                                   |           |  |  |

Table One. SC32 instruction set.

| Primitive | SC32 Instruction                                                    |

|-----------|---------------------------------------------------------------------|

| DUP       | TOS → TOS; ↓P                                                       |

| >R        | TOS $\rightarrow$ TOR; ↑P; $\downarrow$ R                           |

| R>        | $TOR \rightarrow TOS; \uparrow R; \downarrow P$                     |

| OVER      | SOS → TOS; ↓P                                                       |

| 1+        | $TOS + 1 \rightarrow TOS$                                           |

| 1234      | ZERO + 1234 → TOS; ↓P                                               |

| 12345678  | ZERO + 1234 · $2^{16} \rightarrow TOS; \downarrow P$                |

|           | TOS + 5678 → TOS                                                    |

| @         | * $(TOS + 0) \rightarrow TOS$                                       |

| !         | *(TOS + 0) ← TOS; ↑P                                                |

|           | ↑P                                                                  |

| +         | SOS + TOS → TOS; ↑P                                                 |

| <         | SOS — TOS; $N_{yor}V \rightarrow FL \rightarrow TOS$ ; $\uparrow P$ |

| 0=        | $TOS; Z \rightarrow FL \rightarrow TOS$                             |

Table Two. SC32 implementation of some typical Forth primitives.

| Sequence         | SC32 Instruction                                             |

|------------------|--------------------------------------------------------------|

| OVER 1+          | $SOS + 1 \rightarrow TOS; \downarrow P$                      |

| R> +             | TOR + TOS → TOS; ↑R                                          |

| + 0=             | SOS + TOS; $Z \rightarrow FL \rightarrow TOS$ ; $\uparrow P$ |

| AVARIABLE @      | *(ZERO + AVARIABLE) → TOS; ↓P                                |

| OVER @           | *(SOS + 0) → TOS; ↓P                                         |

| OVER ANARRAY + @ | *(SOS + ANARRAY) → TOS; ↓P                                   |

| DUP 9 + @        | *(TOS + 9) → TOS; ↓P                                         |

| BEGIN            |                                                              |

| DUP SIZE < WHILE | ZERO + 8190 $\rightarrow$ TOS; $\downarrow$ P                |

|                  | SOS — TOS; $N_{xor}V \rightarrow FL$ ; $\uparrow P$          |

|                  | conditional branch <forward></forward>                       |

| 0 OVER FLAGS + ! | *(TOS + FLAGS) ← ZERO                                        |

| OVER +           | SOS + TOS → TOS                                              |

| REPEAT           | branch <back></back>                                         |

|                  |                                                              |

Table Three. SC32 object-code compaction.

instruction. DUP, >R, R>, and OVER in Table Two are examples. Primitives that add small (16-bit) constants to TOS (e.g. 1+, 2+, etc.) are implemented with load-address-low. Small literals are created with load-address-low by adding the literal value to the zero register and pushing the result on the parameter stack. Table Two also shows how a large literal is constructed by pushing the most significant part of the number on the stack, then adding in the least significant part. Forth's @ and ! operators are implemented with the load-from-memory and store-to-memory instructions, in the obvious way.

Forth has several arithmetic primitives that operate on the top two parameter stack elements, pop the stack, and write the result to the top of the stack. Examples of such binary operators are +, AND, XOR, etc. These operators are implemented with the micro-instruction. R1 selects the second item on the parameter stack (SOS) as one ALU operand (remember that the other operand is always TOS in micro-instructions). The ALU performs the selected arithmetic or logic operation, the stack is popped, and the result written to TOS. Binary comparison primitives such as <, =, U<, etc. are also implemented with the micro-instruction. Micro has the ability to produce a 32-bit 0 or -1 truth value as the result of a comparison. Unary arithmetic primitives (e.g., NEGATE, 1-, NOT, etc.) and unary comparisons (0<,0=,0>, etc.) can all be realized with one micro-instruction.

By now, the reader should have a good feel for how Forth's primitives are imple-

mented on the SC32. However, this is not the whole story. The SC32 instruction set and data path are more general than the pure stack model needed for Forth. As a result, it is possible to map multiple Forth primitives into a single SC32 instruction. Consider the sequence of primitives OVER 1+. OVER works by sending SOS through the ALU unmodified and pushing the value onto the stack. 1+ now reads this value through the ALU again, this time adding one. The first movement through the ALU is superfluous and can be eliminated by combining OVER 1+ into one instruction.

Table Three has several more compaction examples. Each entry in the table suggests an entire class of compactions. There is an astronomical number of possible combinations. An optimizer written for the SC32\* captures most of the more useful cases. All of the examples in the table, including the last one, were compacted by the optimizer without human intervention. The last example, the inner loop of the Sieve of Eratosthenes [Gil83], was included to test your understanding of the SC32.

### Wrapup

The SC32 microprocessor is fabricated in a two µm CMOS process and packaged in an 84-pin PGA. We are using the SC32 on a number of projects within JHU/APL, the most interesting being the flight computer of a magnetometer processor that is part of a Swedish satellite named Freja. The chip is also available commercially from Silicon Composers in Palo Alto, California.

Our Forth chip-design team consists of Martin E. Fraeman, myself, Susan C. Lee, Robert L. Williams, and Thomas Zaremba. A description of the SC32's predecessors can be found in [Hay87a] or [Hay87b]. A more complete description of the SC32 will appear in [Hay89].

### References

Gilbreath, J., Gilbreath, G. "Eratosthenes Revisited: Once More through the Sieve," January, 193, pp. 283–326.

Golden, J., Moore, C.H., Brodie, L. "Fast processor chip takes its instructions di-

\*[Hay86] describes an optimizer written for our first Forth chip. While its instruction set differs from that of the SC32, the optimization techniques are similar. rectly from Forth," *Electronic Design*, March 21, 1985, pp. 127–138.

Hayes, J.R. "An Interpreter and Object Code Optimizer for a 32-Bit Forth Chip," 1986 FORML Conference Proceedings, pp. 211-221.

Hayes, J.R., Fraeman, M.E., Williams, R.L., Zaremba, T. "An Architecture for the Direct Execution of the Forth Programming Language," Proceedings of the Second Intl. Conf. on Architectural Support for Programming Languages and Operating Systems, pp. 42-49.

Hayes, J.R., Fraeman, M.E., Williams, R.L., Zaremba, T. "A 32-Bit Forth Microprocessor," *Proceedings of the 1987 Rochester Forth Conference*, pp. 39-48.

Hayes, J.R., Lee, S.C. "Stack Caching in the SC32 Forth Processor," 1988 FORML Conference Proceedings, pp. 100–104.

Hayes, J.R., Lee, S.C. "The Architecture of the SC32 Forth Engine," *Journal of Forth Application and Research* 5,4 (to appear).

Ritter, T., Walker, G. "Varieties of Threaded Code for Language Implementation," *BYTE* 5,9, September, 1980, pp. 206–227.

John R. Hayes received an M.S. in computer science from Johns Hopkins University in 1986. He has written flight software in Forth for satellite-based magnetometer experiments and for the shuttle-based Hopkins Ultraviolet Telescope. He is currently applying the SC32 in a variety of projects.

### **NGS FORTH**

A FAST FORTH, OPTIMIZED FOR THE IBM PERSONAL COMPUTER AND MS-DOS COMPATIBLES.

### STANDARD FEATURES INCLUDE:

- •79 STANDARD

- •DIRECT I/O ACCESS

- •FULL ACCESS TO MS-DOS FILES AND FUNCTIONS

- •ENVIRONMENT SAVE & LOAD

- •MULTI-SEGMENTED FOR LARGE APPLICATIONS

- •EXTENDED ADDRESSING

- ●MEMORY ALLOCATION CONFIGURABLE ON-LINE

- •AUTO LOAD SCREEN BOOT

- •LINE & SCREEN EDITORS

- •DECOMPILER AND DEBUGGING AIDS

- ●8088 ASSEMBLER

- •GRAPHICS & SOUND

- NGS ENHANCEMENTS

- **•DETAILED MANUAL**

- •INEXPENSIVE UPGRADES

- ONGS USER NEWSLETTER

A COMPLETE FORTH DEVELOPMENT SYSTEM.

### PRICES START AT \$70

NEW→HP-150 & HP-110 VERSIONS AVAILABLE

NEXT GENERATION SYSTEMS P.O.BOX 2987 SANTA CLARA, CA. 95055 (408) 241-5909

### PHASE ANGLE DIFFERENCE ANALYZER

C.H. TING - SAN MATEO, CALIFORNIA

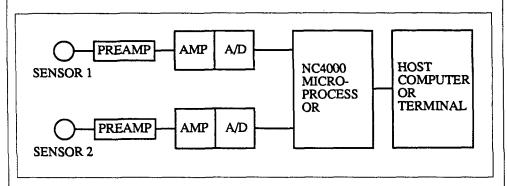

he Phase Angle Difference Analyzer is an instrument which can determine accurately the time delay and phase difference between two analog signals sampled simultaneously by two sensors. The signals are digitized by two fast A/D converters and the results are analyzed by an NC4000 microprocessor. The frequency range of the input signals is from 20 Hz to 20 KHz, and the accuracy is about 0.05 degrees. It is especially useful for direction-finding based on acoustic waves.

### Introduction

The Phase Angle Difference Analyzer (PANDA) measures the phase difference between two channels of analog inputs, assuming that the inputs are generated by the same source with different time delays between the two channels. This method is very similar to correlation analysis, but much simpler and faster.

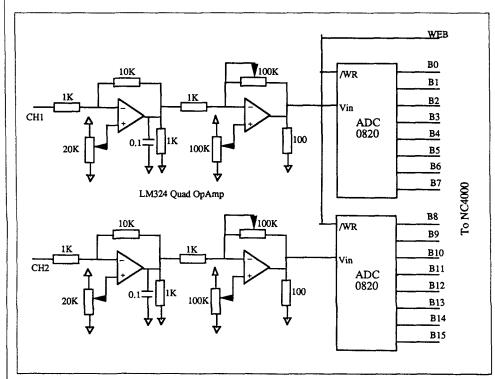

Figure One shows a block diagram of the PANDA system. The signals received by two identical sensors are amplified and digitized by two analog-to-digital (A/D) converters. The digital outputs of the A/D converters are then fed into a microprocessor. The microprocessor analyzes the two channels of signal and determines the phase angle difference between the two channels.

A large number of samples are taken by the A/D converters and are stored in two arrays in the computer's memory. The time difference between the two input channels is computed by shifting and comparing values in the two arrays. The point of minimal difference is then interpolated and used to compute the phase difference. This analysis procedure is similar to a correlation analysis. However, the comparing step involves only subtraction, absolution, and addition. By avoiding multiplication, as required in conventional correlation analysis, the computation can be greatly accelerated to allow the PANDA system to perform phase measurements in real time.

The most crucial components in the PANDA system are the A/D converters, since their sampling rate determines the upper frequency of PANDA operation. It is assumed that the microprocessor can read the output from the A/D converters and store the sample data in memory. The upper frequency limit of PANDA was 20 KHz. To analyze an input signal of 20 KHz, PANDA must sample at a rate of 400 KHz so that it can determine the phase difference to the order of 0.1 degree.

### PANDA must sample at a rate of 400 KHz.

Most commercial microprocessors, including rather sophisticated 16-bit machines like the Intel 8086 and Motorola 68000, cannot read data at this required sampling rate. Most data acquisition systems built for commercial microcomputers have an upper sampling rate of about 20 KHz and are not suitable for PANDA. A special CMOS 16-bit microprocessor, the NC40001 invented by Mr. Charles H. Moore, was thus chosen as the CPU for this PANDA. An NC4000 running at a clock of 4 MHz can perform 16-bit input/output at 4 MHz. To store data obtained from the I/O port takes two clock cycles. It is thus potentially capable of acquiring data at a speed exceeding 1 MHz. Two high-speed flash A/ D converters, National ADC 0820, are used to digitize simultaneously the two input channels. A maximum conversion rate of an ADC 0820 is 1 MHz, which matches rather well with the NC4000.

The required sampling rate depends upon the frequency of the input signal. Generally, it is necessary to sample at least 20 times within one wave period. The total number of samples collected into memory is limited to 120 pairs due to memory and real-time processing requirements and limitations. Too few samples within one period would cause aliasing, and thus limit the range of angles in which the correct phase difference can be computed. Too many samples within one period would increase the error of measurement because the sampled array might not cover enough periods to compensate for the truncation of waves at the end of the sampling array. About ten periods are needed to give good accuracy.

### Phase Difference Analysis

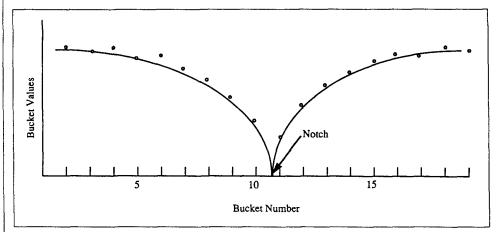

As mentioned above, the method adopted in PANDA to analyze the phase difference between the two input waves is closely related to the conventional correlation analysis. Figure Two shows schematically how the PANDA analysis is carried out. Two channels of input waves are sampled by the A/D converters and the sampled data are stored in two memory arrays, A and B. The data are represented

$$A_0 \ A_1 \ A_3 \dots A_{119}$$

$B_0 \ B_2 \ B_3 \dots B_{119}$

difference sums (bucket values) are computed. The bucket values are equivalent to the results of a correlation analysis:

$$\begin{array}{l} \textbf{S}_{0} \ \textbf{S}_{1} \ \textbf{S}_{2} \dots \textbf{S}_{19} \\ \textbf{S}_{i} = \textbf{SUM} \ | \textbf{A}_{j} \ - \ \textbf{B}_{j+1-10} | \\ \textbf{j} = \textbf{0} \ \textbf{to} \ \textbf{109} \end{array}$$

### HARVARD SOFTWORKS

### NUMBER ONE IN FORTH INNOVATION

(513) 748-0390 P.O. Box 69, Springboro, OH 45066

### MEET THAT DEADLINE!!!

- Use subroutine libraries written for other languages! More efficiently!

- Combine raw power of extensible languages with convenience of carefully implemented functions!

- Yes, it is faster than optimized C!

- Compile 40,000 lines per minute!

- Stay totally interactive, even while compiling!

- Program at any level of abstraction from machine code thru application specific language with equal ease and efficiency!

- Alter routines without recompiling!

- Use source code for 2500 functions!

- Use data structures, control structures, and interface protocols from any other language!

- Implement borrowed feature, often more efficiently than in the source!

- Use an architecture that supports small programs or full megabyte ones with a single version!

- Forget chaotic syntax requirements!

- Outperform good programmers stuck using conventional languages!

(But only until they also switch.)

# HS/FORTH with FOOPS - The only flexible full multiple inheritance object oriented language under MSDOS!

Seeing is believing, OOL's really are incredible at simplifying important parts of any significant program. So naturally the theoreticians drive the idea into the ground trying to bend all tasks to their noble mold. Add on OOL's provide a better solution, but only Forth allows the add on to blend in as an integral part of the language and only HS/FORTH provides true multiple inheritance & membership.

Lets define classes BODY, ARM, and ROBOT, with methods MOVE and RAISE. The ROBOT class inherits: INHERIT> BODY

HAS> ARM RightArm HAS> ARM LeftArm

If Simon, Alvin, and Theodore are robots we could control them with:

Alvin 's RightArm RAISE or:

+5 -10 Simon MOVE or:

+5 -10 Simon MOVE +5 +20 FOR-ALL ROBOT MOVE

Now that is a null learning curve!

### WAKE UP!!!

Forth is no longer a language that tempts programmers with "great expectations", then frustrates them with the need to reinvent simple tools expected in any commercial language.

### **HS/FORTH Meets Your Needs!**

Don't judge Forth by public domain products or ones from vendors primarily interested in consulting they profit from not providing needed tools! Public domain versions are cheap - if your time is worthless. Useful in learning Forth's basics, they fail to show its true potential. Not to mention being s-l-o-w.

We don't shortchange you with promises. We provide implemented functions to help you complete your application quickly. And we ask you not to shortchange us by trying to save a few bucks using inadequate public domain or pirate versions. We worked hard coming up with the ideas that you now see sprouting up in other Forths. We won't throw in the towel, but the drain on resources delays the introduction of even better tools. Don't kid yourself, you are not just another drop in the bucket, your personal decision really does matter. In return, we'll provide you with the best tools money can buy.

### The only limit with Forth is your own imagination!

You can't add extensibility to fossilized compilers. You are at the mercy of that language's vendor. You can easily add features from other languages to HS/FORTH. And using our automatic optimizer or learning a very little bit of assembly language makes your addition zip along as well as in the parent language.

Speaking of assembly language, learning it in a supportive Forth environment turns the learning curve into a light speed escalator. People who failed previous attempts to use assembly language, conquer it in a few hours or days using HS/FORTH.

HS/FORTH runs under MSDOS or PCDOS, or from ROM. Each level includes all features of lower ones. Level upgrades: \$25. plus price difference between levels. Sources code is in ordinary ASCII text files.

All HS/FORTH systems support full megabyte or larger programs & data, and run faster than any 64k limited ones even without automatic optimization -- which accepts almost anything and accelerates to near assembly language speed. Optimizer, assembler, and tools can load transiently. Resize segments, redefine words, eliminate headers without recompiling. Compile 79 and 83 Standard plus F83 programs.

### STUDENT LEVEL

text & scaled/clipped graphics in bit blit windows, mono, cga, ega, vga, fast ellipses, splines, bezier curves, arcs, fills, turtles; powerful parsing, formatting, file and device I/O; shells; interrupt handlers; call high level Forth from interrupts; single step trace, decompiler; music; compile 40,000 lines per minute, stacks;

compile 40,000 lines per minute, stacks; file search paths; formats into strings.

PERSONAL LEVEL \$245.

software floating point, trig, transcendental, 18 digit integer & scaled integer math; vars: A B \* IS C compiles to 4 words, 1..4 dimension var arrays; automatic optimizer-machine code speed.

PROFESSIONAL LEVEL \$395.

hardware floating point - data structures for all data types from simple thru complex 4D var arrays - operations complete thru complex hyperbolics; turnkey, seal; interactive dynamic linker for foreign subroutine libraries; round robin & interrupt driven multitaskers; dynamic string manager; file blocks, sector mapped blocks; x86&7 assemblers.

PRODUCTION LEVEL \$495.

Metacompiler: DOS/ROM/direct/indirect; threaded systems start at 200 bytes, Forth cores at 2 kbytes; C data structures & struct+ compiler; TurboWindow-C MetaGraphics library, 200 graphic/window functions, PostScript style line attributes & fonts, viewports.

### PROFESSIONAL and PRODUCTION LEVEL EXTENSIONS:

FOOPS+ with multiple inheritance\$ 75. 286FORTH or 386FORTH \$295.

16 Megabyte physical address space or gigabyte virtual for programs and data; DOS & BIOS fully and freely available; 32 bit address/operand range with 386. BTRIEVE for HS/FORTH (Novell) \$199. ROMULUS HS/FORTH from ROM\$ 95. FFORTRAN translator/mathpak \$75. Compile Fortran subroutines! Formulas, logic, do loops, arrays; matrix math, FFT, linear equations, random numbers.

Figure One. Block diagram of PANDA system.

Figure Two. Analysis of phase difference.

Figure Three. Analog and A/D circuitry in PANDA system.

If the two channels are identical, it is obvious that  $S_{10}$  should be zero and that it is the smallest of the 20 bucket values, because all the difference terms in this sum are zero. Values neighboring  $S_{10}$  should increase gradually, forming a notch at  $S_{10}$  when the bucket values are plotted against the bucket number. The phase difference between the two input channels can be determined accurately by how much the notch shifts away from the  $S_{10}$ , as shown in Figure Two.

A simple interpolation algorithm is applied to determine the true notch-bucket number, which is related to the time difference of signal arrival at the two sensors. If the *i*th bucket has the lowest bucket value S<sub>i</sub>, the true notch is calculated from the following equation:

NOTCH =

$$i + (S_{i-1} - S_{i+1}) / 2(S_{i-1} + S_{i+1} - 2S_i)$$

An equation for BASELINE is as follows:

BASELINE =

$$D/(delta * V)$$

where D is the distance between the two sensors, delta is the sampling time, and V is the speed of signal. The angle-of-arrival (AOA) is then:

In the present PANDA system, the sampling time of the A/D converter is programmable through the system variable DELAY. The relationship between DELAY and delta is:

delta =

$$0.25$$

(DELAY+11)  $\mu$ sec.

The NC4000 processor cycle is 0.25 microseconds using a 4 MHz clock. It takes 11 cycles to start the A/D converters, wait until the data is digitized, input the data, and store the data to memory.

### Hardware

The PANDA main unit consisted of two circuit boards, one analog and one digital. The analog processing board contained a pair of OpAmp circuits to amplify and condition the input signals, and a pair of fast A/D converters to digitize the sensor input signal. The digital processing board contained the main CPU chip (NC4000),

EPROM, and SRAM memory chips, and digital I/O circuitry. The CPU analyzes the input signals and sends the results to a terminal (Qume QVT-102) or to a host computer for archiving and displaying tasks.

Figure Three shows the schematics of the analog board. The amplifier/signal-conditioners are constructed with a single quad OpAmp IC (National LM324). Each single channel uses two OpAmps, one for input conditioning with a gain of ten, and another for amplification and offset adjustment to present the signals optimized for the A/D converter. The amplifier stage has an adjustable gain of 0.1 to 100, and an offset range of 0–5 volts.

Two A/D converters are used in parallel to convert simultaneously the two channels of sensor signals in order to increase the conversion throughput and to avoid skewing in the sampling process.<sup>2</sup> The A/D converters are eight-bit half-flash converters. The start-conversion clock is provided by an I/O write-enable (WEB) signal from the MC4000, and the output data are read by the NC4000 through the B port. Each A/D provides eight bits of data to the 16-bit B

port. Although the A/D converters and the SPU are capable of running up to a 1 MHz sampling rate, due to the start-conversion and memory-storing overhead in the data acquisition process, the maximum practical sampling rate is 400 KHz on both channels.

The digital processor board is a CMOS single-board microprocessor (Silicon Composers SC1000-CPU). It contains a very fast CMOS 16-bit microprocessor (Novix NC4000). This CPU executes one CPU instruction in every clock cycle derived from a 4 MHz single-phase clock. All branch and subroutine-call instructions are also completed in one clock cycle. Memory access requires two cycles. This speed allowed the PANDA to obtain and analyze data from the A/D converters at the rate required by the PANDA experiments.

Surrounding the NC4000 chip are two eight Kbyte EPROM memory chips hosting the PANDA software, two 32 Kbyte RAM chips for data storage, and four eight Kbyte RAM chips serving as one data stack and one return stack. A few MSI glue chips complete the processor board: a 74HC138 for memory decoding, a CD4050 for reset and serial I/O buffering, and a 4 MHz

CMOS clock.

Two bits in the X I/O port on the NC4000 are used to emulate an RS-232 serial interface port, which allows the NC4000 to communicate with a terminal or host computer. Only the transmit and receive lines are used in this RS-232 interface. The data format is 9600 baud, eight data bits, and one stop bit. Parity is disabled. The transmit and receive lines are buffered through the CD4050.

The digital and analog boards are connected through a bussed backplane. Although all the memory and I/O signals are brought out to the backplane, the analog processor uses only the B port I/O signals.

### Software

The software installed in the PANDA system controls the operations of the system and its user-host interface. It allows the user to specify the conditions under which the PANDA system is to be operated, such as the sampling rate, the time delay between data reports, and the format of the data reports. It also allows a host computer to receive the results and to process the raw data with more sophisticated data analysis

# Total control with LMI FORTH™

For Programming Professionals: an expanding family of compatible, highperformance, compilers for microcomputers

### For Development:

Interactive Forth-83 Interpreter/Compilers for MS-DOS, OS/2, and the 80386

- 16-bit and 32-bit implementations

- · Full screen editor and assembler

- Uses standard operating system files

- 500 page manual written in plain English

- Support for graphics, floating point, native code generation

### For Applications: Forth-83 Metacompiler

- · Unique table-driven multi-pass Forth compiler

- Compiles compact ROMable or disk-based applications

- Excellent error handling

- Produces headerless code, compiles from intermediate states, and performs conditional compilation

- Cross-compiles to 8080, Z-80, 8088, 68000, 6502, 8051, 8096, 1802, 6303, 6809, 68HC11,34010, V25, RTX-2000

- No license fee or royalty for compiled applications

## Thinking of using the Zilog Forth Super8 Chip?

Inner Access has FORTH Super8 development tools for you!

- Development Lab

- Metacompiler

- Development ROMS

with F83 based terminal emulation and file server software for the IBM

Inner Access Corporation Box 888 Belmont CA 94002 (415) 591-8295

```

( PANDA SETUP, 10AUG86CHT )

HEX

3CO CONSTANT RESULTS

( Bucket values )

400 CONSTANT 1TEST

( Primary data array )

( Second data array )

A00 CONSTANT 2TEST

O CONSTANT COUNTER

( Report counter )

1 CONSTANT DELAY

( Delay between samples )

( Delay between reports )

2 CONSTANT WAITING

3 CONSTANT RADIUS

( Baseline between sensors )

( Number of A/D samples )

4 CONSTANT SAMPLES

5 CONSTANT FREQUENCY

(Frequencey multiplier)

6 CONSTANT PHASE

( Phase offset )

7 CONSTANT TICKS

DECIMAL

: ONE-PASS ( PHASE -- SUM )

( Initial sum )

( Analyze only 100 samples )

SAMPLES @ 20 -

FOR OVER 1TEST + I + @ (Channel 1 data with offset)

( Channel 2 data )

2TEST I + 10 + @

( Subtract, absolute, accumulate )

- ABS +

NEXT

SWAP DROP

: 20-PASSES ( -- )

1 COUNTER +!

( Increment report count )

RESULTS 20 ERASE

( Clear sum array )

19 FOR

I ONE-PASS